ついに半導体枯渇が死活問題になってきた

ある程度の在庫を抱えてはいたのですが、Cyclone 10LP/MAX10が枯渇しそうです。

少なくともトレイに入った状態のintel FPGAはここ半年くらいお目にかかっていません。在庫しているボードものこりがわずかで、使い終わったらおしまい。商社によると年末に各社から不良在庫回避放出イベントが多少あるんじゃないか、と言われてましたがそうでもなさそう。

そんな経緯で、代替デバイスを検討すべく小規模FPGAに限って新興メーカ数社を中心に評価ボード、供給体制をチェックしていました。とはいえ弊社との取引先に無断でメインコアを変えるわけにも行かないので、対応を長いこと協議していました。

ADAS向けとシニアカーなどの福祉車両向けがメインです。車載グレードが必ずしも要求されない用途に限ります。

複数のデバイスを調査していますが、早い段階からチェックしていたQuickLogic EOS S3は、私(ハードウェア担当)が選択肢から外そうとしていました。詳細は後述しますが、いわゆるFPGAに求める機能があまりにも欠落しているかな、、、という判断でした。

ですが、取引先の大半のエンジニア(ソフトウェア担当)が違う観点でした。

下記は協議中に挙げられたメリットデメリットです。

基板の設計にあたって

チップの在庫確保もでき問題なさそうです。

問題はハードウェアチームです。基板製造コストがintelFPGAに比べかなり上がるのと、intelFPGAほどの機能が見込めないので妥協案を探っていきます。

- PLLがない問題

頼りにしていたSi5351Aがしばらく枯渇しています。L/Tみても絶望しかありません。

これについてはPLLで何がしたいか、という問題を検討しました。多くの場合数百MHzのクロックが欲しいのではなく、数十MHzのクロックとその90度位相が遅れたクロック(I-Q)が欲しいだけです。ですので、ロジック回路で解決できそうです。高速動作する74AVC74などに欲しい周波数の4倍を加え、I,Qを取得する算段にします。なお、FPGA側でそのくらいは作れそうに思えますが、ループエラーで論理合成は成功しないと思われます。そもそもFmaxが低いのでそれ以前の問題ですが。

- 基板製造価格

製造費用増は仕方がありません。事前検討の結果、EOS S3のBGA64ピンのうち62ピンはどうしても必要なことがわかっています。

パッドオンビアかつビルドアップを選択しますが、べリードビアを避ける、フルスタックではなく貫通viaにする(4-layer ,1−2−1 BHなし)ことによりなるべく費用を下げます*2

- SRAMが足りない問題

外付けでQSPI IoT SRAMを使用します。EOS S3のFmaxがかなり低いことも検討の結果わかっていますので、帯域を確保するため2個パラレルで使用します。この時必要になるGPIOは12pin(=6pin x 2個)です。パラレルSRAMを使用する場合より格段に少ないピン数です。

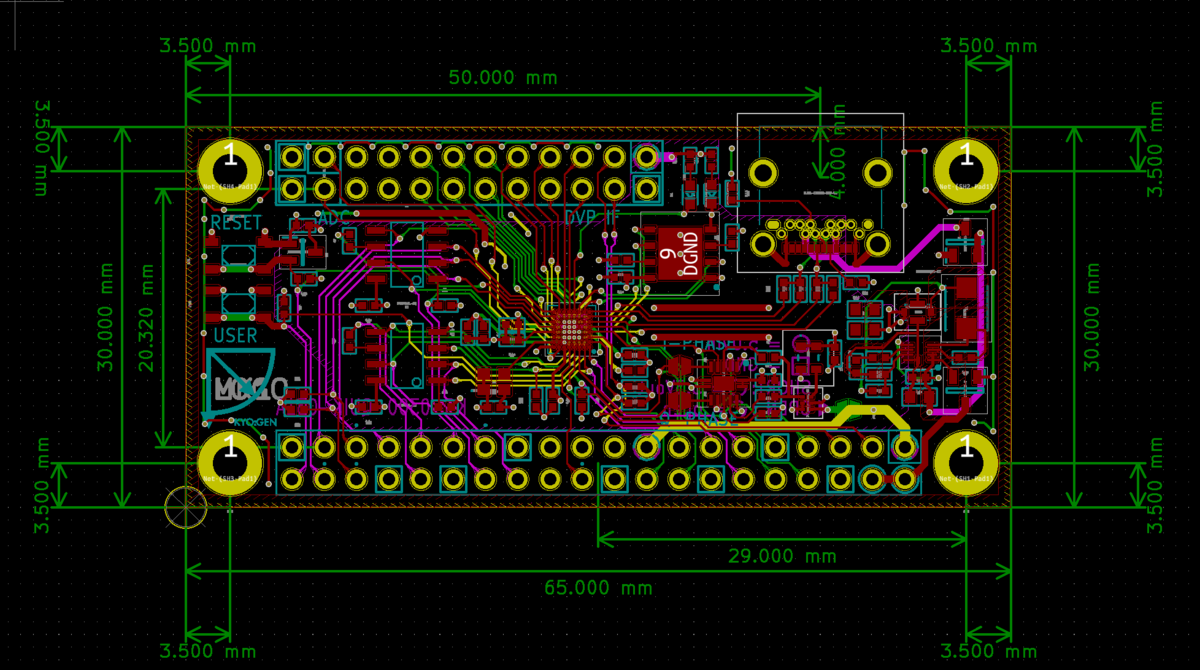

基板外観

こんな感じ。アートワークは2日ほどで終わりました。部品選定は選定中に商社から在庫が消えるという体験を何回もやっているので4日ほどかかっています。もうやだー。

裏面

何も部品は配置しません。*3シルクで電源端子の説明だけ書いておきます。

部品点数自体は少ないので、4層もあれば広々と配置できます。

見ての通り、Raspberry Pi ZeroのHATと同じフットプリントです。デバッグはすべてラズパイから行います。

部品も確保済み。ガーバーアウトしたので、あとは製造実装まちです。